US010713996B2

### (12) United States Patent Kim et al.

### (54) **DISPLAY PANEL AND METHOD FOR DRIVING THE DISPLAY PANEL**

(71) Applicants: SAMSUNG ELECTRONICS CO.,

LTD., Suwon-si (KR); RESEARCH &

BUSINESS FOUNDATION

SUNGKYUNKWAN UNIVERSITY,

Suwon-si (KR)

(72) Inventors: Jinho Kim, Suwon-si (KR); Yongsang Kim, Suwon-si (KR); Sangmin Shin, Suwon-si (KR); Jongsu Oh, Suwon-si (KR); Youngki Jung, Suwon-si (KR)

(73) Assignees: SAMSUNG ELECTRONICS CO., LTD., Suwon-si (KR); RESEARCH & BUSINESS FOUNDATION SUNGKYUNKWAN UNIVERSITY,

Suwon-si (KR)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

(21) Appl. No.: 16/263,253

(22) Filed: Jan. 31, 2019

(65) Prior Publication Data

US 2020/0111403 A1 Apr. 9, 2020

(30) Foreign Application Priority Data

Oct. 4, 2018 (KR) ...... 10-2018-0118317

(51) Int. Cl. *G09G 3/20* (2006.01) *H01L 27/15* (2006.01)

**H01L 27/15** (2006.01) **G09G 3/32** (2016.01)

(52) **U.S. Cl.** CPC ....... *G09G 3/2011* (2013.01); *G09G 3/2003* (2013.01); *G09G 3/2014* (2013.01);

(Continued)

(10) Patent No.: US 10,713,996 B2

(45) **Date of Patent:** Jul. 14, 2020

### (58) Field of Classification Search

CPC .. G09G 3/2011; G09G 3/2003; G09G 3/2014; G09G 3/32; G09G 2300/0426;

(Continued)

### (56) References Cited

### U.S. PATENT DOCUMENTS

5,206,633 A 4/1993 Zalph 5,561,441 A 10/1996 Hamano (Continued)

#### FOREIGN PATENT DOCUMENTS

JP 2018-503880 A 2/2018 JP 6278626 B2 2/2018 (Continued)

### OTHER PUBLICATIONS

International Search Report (PCT/ISA/210) dated May 17, 2019 issued by the International Searching Authority in International Application No. PCT/KR2019/001359.

(Continued)

Primary Examiner — Andrew Sasinowski (74) Attorney, Agent, or Firm — Sughrue Mion, PLLC

### (57) ABSTRACT

A display panel is provided. In the display panel, a plurality of pixels respectively including a plurality of sub pixels are arranged in a matrix form on a glass. Each of the plurality of sub pixels includes a driving circuit disposed on the glass and configured to receive a PAM data voltage and a PWM data voltage, and an inorganic light emitting device configured to emit a light based on a driving current provided from the driving circuit. The PAM data voltage is applied at once to the plurality of pixels included in the display panel. The driving circuit compensates a deviation between driving circuits included in each of the plurality of sub pixels based on a driving voltage of the driving circuit, and controls a (Continued)

pulse width of a driving current having an amplitude corresponding to the applied PAM data voltage based on the applied PWM data voltage.

### 20 Claims, 17 Drawing Sheets

###

### (58) Field of Classification Search

CPC ..... G09G 2310/0202; G09G 2300/043; G09G 2300/0819; G09G 2300/0452; G09G 2320/0633; G09G 2310/08; H01L 27/156 See application file for complete search history.

### (56) References Cited

### U.S. PATENT DOCUMENTS

| 7,167,169    | B2  | 1/2007  | Libsch et al.       |

|--------------|-----|---------|---------------------|

| 7,623,123    |     |         | Kim                 |

| 7,675,249    |     | 3/2010  | Furukawa et al.     |

| 7,808,497    |     |         | Lo et al.           |

| 8,289,349    |     | 10/2012 | Kobayashi           |

| 8,569,975    |     | 10/2013 | Uchimoto et al.     |

| 10.504,406   |     | 12/2019 | Shigeta et al.      |

| 2005/0168417 |     | 8/2005  | Ha et al.           |

| 2006/0158396 |     | 7/2006  | Jo                  |

| 2006/0198330 |     | 12/2006 | Ishida              |

| 2008/0007496 |     | 1/2008  | Kim et al.          |

| 2008/0007490 |     | 9/2008  | Kwok et al.         |

| 2009/0021178 |     | 1/2009  | Furukawa H05B 45/20 |

| 2009/0021178 | AI. | 1/2009  |                     |

|              |     |         | 315/250             |

| 2009/0115703 |     | 5/2009  | Cok                 |

| 2010/0188443 | A1* | 7/2010  | Lewis G02B 26/02    |

|              |     |         | 345/691             |

| 2010/0309100 | A1  | 12/2010 | Cok et al.          |

| 2011/0279444 | A1  | 11/2011 | Chung et al.        |

| 2011/0298820 | A1* | 12/2011 | Hajjar G02B 26/123  |

|              |     |         | 345/619             |

| 2012/0086734 | A1* | 4/2012  | Kitani G09G 3/22    |

|              |     | . 2012  | 345/690             |

|              |     |         | 373/030             |

| 2012/0113083 | A1*           | 5/2012  | Kim G09G 3/344             |

|--------------|---------------|---------|----------------------------|

| 2012/0169777 | A1*           | 7/2012  | 345/212<br>Budni G09G 3/02 |

|              |               |         | 345/690                    |

| 2013/0009938 | A1            | 1/2013  | Hwang et al.               |

| 2014/0362062 | A1            | 12/2014 | Limketkai et al.           |

| 2016/0139416 | $\mathbf{A}1$ | 5/2016  | Yamakawa et al.            |

| 2016/0314741 | $\mathbf{A}1$ | 10/2016 | Yin                        |

| 2017/0263183 | A1            | 9/2017  | Lin et al.                 |

| 2018/0144717 | A1            | 5/2018  | Kim et al.                 |

| 2018/0151132 | A1*           | 5/2018  | Lee G09G 3/30              |

| 2018/0182279 | A1*           | 6/2018  | Sakariya G09G 3/2014       |

| 2018/0301080 | A1            | 10/2018 | Shigeta et al.             |

| 2019/0304386 | $\mathbf{A}1$ | 10/2019 | Kim et al.                 |

| 2019/0371231 | $\mathbf{A}1$ | 12/2019 | Kim et al.                 |

| 2019/0371232 | A1            | 12/2019 | Kim et al.                 |

|              |               |         |                            |

#### FOREIGN PATENT DOCUMENTS

| KR | 10-0914929 B1     | 9/2009 |

|----|-------------------|--------|

| KR | 10-2015-0015637 A | 2/2015 |

| KR | 10-1773614 B1     | 8/2017 |

| KR | 10-2018-0002786 A | 1/2018 |

| KR | 10-2018-0057073 A | 5/2018 |

| WO | 2018053025 A1     | 3/2018 |

### OTHER PUBLICATIONS

Written Opinion (PCT/ISA/237) dated May 17, 2019 issued by the International Searching Authority in International Application No. PCT/KR2019/001359.

International Search Report (PCT/ISA/210) dated Jul. 3, 2019 issued by the International Searching Authority in International Application No. PCT/KR2019/001343.

Written Opinion (PCT/ISA/237) dated Jul. 3, 2019 issued by the International Searching Authority in International Application No. PCT/KR2019/001343.

International Search Report (PCT/ISA/210) dated Jul. 3, 2019 issued by the International Searching Authority in International Application No. PCT/KR2019/001357.

Written Opinion (PCT/ISA/237) dated Jul. 3, 2019 issued by the International Searching Authority in International Application No. PCT/KR2019/001357.

Communication dated Apr. 27, 2020 issued by the United States Intellectual Property Office in counterpart U.S. Appl. No. 16/263,901. Communication dated Mar. 2, 2020 issued by the United States Intellectual Property Office in counterpart U.S. Appl. No. 16/263,271.

<sup>\*</sup> cited by examiner

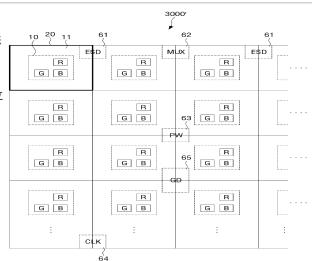

# FIG. 2A

1000

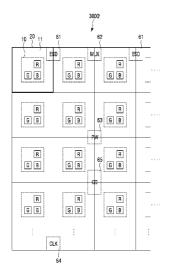

## FIG. 2B

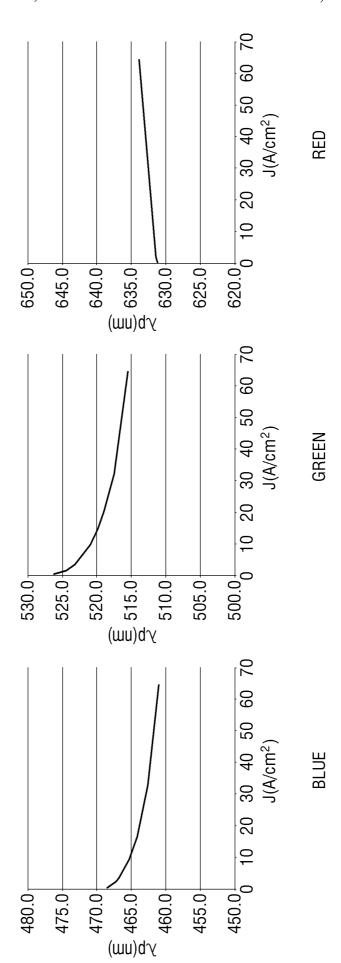

FIG. 3

FIG. 4

FIG. 5

FIG. 6

# FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11B

# FIG. 12A

10000

FIG. 12B

FIG. 13

### FIG. 14

### DISPLAY PANEL AND METHOD FOR DRIVING THE DISPLAY PANEL

### CROSS-REFERENCE TO RELATED APPLICATION

This application is based on and claims priority under 35 U.S.C. § 119(a) of a Korean Patent Application number 10-2018-0118317, filed on Oct. 4, 2018, in the Korean Intellectual Property Office, and the disclosure of which is incorporated by reference herein in its entirety.

#### **BACKGROUND**

#### 1. Field

The disclosure relates to a display panel and a method for driving the display panel. More particularly, the disclosure relates to a display panel in which light emitting devices are included in a pixel, and a method for driving the display panel.

### 2. Description of Related Art

In related art, a display panel driving an inorganic light emitting device (hereinafter referred to as "LED") such as a red LED, a green LED, and a blue LED, as a sub pixel expresses a grayscale or gradation of a sub pixel through a pulse amplitude modulation (PAM) drive method.

In this case, a wavelength as well as a grayscale or gradation of a light emitted is shifted together according to an amplitude of the driving current, and thereby a color reproducibility of an image is reduced. FIG. 1 illustrates wavelength shifts according to a magnitude or an amplitude of a driving current flowing through a blue LED, a green LED, and a red LED.

The above information is presented as background information only to assist with an understanding of the disclosure. No determination has been made, and no assertion is made as to whether any of the above description may be applicable as prior art with regard to the disclosure.

### **SUMMARY**

Aspects of the disclosure are to address at least the above-mentioned problems and/or disadvantages and to provide at least the advantages described below. Accordingly, an aspect of the disclosure is to provide a display panel 50 providing improved color reproducibility to an input image signal through an LED which is an inorganic light emitting device mounted on a glass substrate, and a method for driving the display panel.

Another aspect of the disclosure is to provide a display 55 panel including a driving circuit capable of more efficiently driving an LED which is an inorganic light emitting device mounted on a glass substrate, and a method for driving the display panel.

Another aspect of the disclosure is to provide a display 60 panel including a driving circuit appropriate for a high-density integrated circuit by optimizing a design of a driving circuit driving an LED which is an inorganic light emitting device mounted on a glass substrate, and a method for driving the display panel.

Another aspect of the disclosure is to provide a display panel including a driving circuit capable of stably operating 2

an LED which is an inorganic light emitting device mounted on a glass substrate, and a method for driving the display panel.

In accordance with an aspect of the disclosure, a display panel is provided. In the display panel, a plurality of pixels respectively including a plurality of sub pixels are arranged in a matrix form on a glass. Each of the plurality of sub pixels includes a driving circuit disposed on the glass and configured to receive a pulse amplitude modulation (PAM) data voltage and a pulse width modulation (PWM) data voltage, and an inorganic light emitting device mounted on the driving circuit and configured to be electrically connected to the driving circuit, and to emit a light based on a driving current provided from the driving circuit. The PAM data voltage is applied at once to the plurality of pixels included in the display panel. The driving circuit is configured to control a grayscale of a light emitted by the inorganic light emitting device by compensating a deviation between driving circuits included in each of the plurality of sub pixels based on a driving voltage of the driving circuit and controlling a pulse width of a driving current having an amplitude corresponding to the applied PAM data voltage based on the applied PWM data voltage.

The driving circuit may include a PAM driving circuit including a first driving transistor and configured to control amplitude of the driving current based on the applied PAM data voltage, and a PWM driving circuit including a second driving transistor and configured to control a pulse width of the driving current based on the applied PWM data voltage. The deviation between the driving circuits may be a deviation of threshold voltage between first driving transistors included in each of the plurality of sub pixels, and a deviation of threshold voltage between second driving transistors included in each of the plurality of sub pixels.

The PAM driving circuit may be configured to, based on the driving voltage being applied, apply a first voltage based on the driving voltage and a threshold voltage of the first driving transistor to a gate terminal of the first driving transistor. The PWM driving circuit may be configured to, based on the driving voltage being applied, apply a second voltage based on the driving voltage and a threshold voltage of the second driving transistor to a gate terminal of the second driving transistor.

The PAM driving circuit may be configured to, after a gate terminal voltage of the first driving transistor being equal to the first voltage, based on the PAM data voltage being applied, apply a third voltage based on the first voltage and the PAM data voltage to the gate terminal of the first driving transistor. The PWM driving circuit may be configured to, after a gate terminal voltage of the second driving transistor being equal to the first voltage, based on the PWM data voltage being applied, apply a fourth voltage based on the second voltage and the PWM data voltage to the gate terminal of the second driving transistor. The driving circuit may be configured to, based on the driving voltage being applied to the inorganic light emitting device through the first driving transistor and a linearly-changing sweep signal being applied to the PWM driving circuit, provide a driving current of an amplitude corresponding to the applied PAM data voltage to the inorganic light emitting device from a time when the driving voltage is applied to the inorganic light emitting device until a time when the fourth voltage applied to the gate terminal of the second driving transistor is linearly shifted according to the sweep signal and becomes the second voltage.

The PWM data voltage may be sequentially applied to the plurality of pixels for each line of the plurality of pixels arranged in the matrix form.

The PAM data voltage applied at once to the plurality of sub pixels may be a voltage of the same magnitude.

The display panel may be divided into a plurality of areas. The PAM driving circuit may receive the PAM data voltage for each of the plurality of areas.

A PAM data voltage applied to at least one area for driving a high dynamic range (HDR) from among the plurality of areas may be different from a PAM data voltage applied to other areas of the plurality of areas.

The plurality of sub pixels may include an R sub pixel including an inorganic light emitting device emitting a red (R) light, a G sub pixel including an inorganic light emitting 15 device emitting a green (G) light, and a B sub pixel including an inorganic light emitting device emitting a blue (B) light.

The inorganic light emitting device may be a micro-LED (micro Light Emitting Diode) having a magnitude of less than or equal to 100 micrometers.

The PAM driving circuit may include a first transistor which is connected to and disposed between a drain terminal of the first driving transistor and the gate terminal of the first driving transistor, a first capacitor including a first terminal commonly connected to a source terminal of the first driving 25 transistor, a source terminal of the second driving transistor, and a driving voltage terminal of the driving circuit, a second capacitor including a first terminal commonly connected to the gate terminal of the first driving transistor, a second terminal of the first capacitor, and a source terminal 30 of the first transistor, and a second transistor including a source terminal via which the PAM data voltage is applied, and a drain terminal connected to a second terminal of the second capacitor.

The PAM driving circuit may be configured to, while the 35 first transistor is turned on, based on the driving voltage being applied via the driving voltage terminal, apply the first voltage corresponding to a sum of the driving voltage and the threshold voltage of the first driving transistor to the gate terminal of the first driving transistor via the turned-on first driving transistor, and based on the PAM data voltage being applied via the source terminal of the second transistor, to apply the third voltage corresponding to a sum of the first voltage and the applied PAM data voltage to a gate terminal of the first transistor.

The PWM driving circuit may include a third transistor which is connected to in between a drain terminal of the second driving transistor and the gate terminal of the second driving transistor, a fourth transistor including a drain terminal connected to the gate terminal of the second driving 50 transistor and a source terminal of the third transistor, a third capacitor including a first terminal commonly connected to the gate terminal of the second driving transistor, the source terminal of the third transistor, and the drain terminal of the fourth transistor, a fifth transistor including a source terminal 55 via which the PWM data voltage is applied, and a drain terminal connected to a second terminal of the third capacitor, and a fourth capacitor including a first terminal commonly connected to the second terminal of the third capacitor and the drain terminal of the fifth transistor, and a second 60 terminal receiving a linearly-shifting sweep signal.

The PWM driving circuit may be configured to, while the third transistor is turned on, based on the driving voltage being applied via a the driving voltage terminal, apply the second voltage corresponding to a sum of the driving obtage and the threshold voltage of the second driving transistor to the gate terminal of the second driving transistor

4

via the turned-on second driving transistor, and based on the PWM data voltage being applied via the source terminal of the fifth transistor, to apply the fourth voltage corresponding to the second voltage and the applied PWM data voltage to the gate terminal of the second transistor.

The driving circuit may further include a sixth transistor including a source terminal commonly connected to the drain terminal of the second driving transistor and a drain terminal of the third transistor, and a drain terminal commonly connected to the gate terminal of the first driving transistor, the second terminal of the first capacitor, the first terminal of the second capacitor, and the source terminal of the first transistor, and a seventh transistor including a source terminal commonly connected to the drain terminal of the first driving transistor and a drain terminal of the first transistor, and a drain terminal connected to an anode terminal of the light emitting device. A cathode terminal of the inorganic light emitting device may be connected to a ground voltage terminal of the driving circuit.

The driving circuit may be configured to drive the PAM driving circuit and the PWM driving circuit independently of each other while the sixth and seventh transistors are turned off, and apply the first voltage and the second voltage to the gate terminal of the first driving transistor and the gate terminal of the second driving transistor, respectively, and while the sixth and seventh transistors are turned on, based on the sweep signal being applied via the fourth capacitor, to drive the PAM driving circuit and the PWM driving circuit together, and until the fourth voltage applied to the gate terminal of the second driving transistor is shifted according to the sweep voltage and becomes the second voltage, provide a driving current of an amplitude corresponding to the applied PAM data voltage to the inorganic light emitting device.

Gate terminal voltages of the first and second driving transistors may be, before the first and second voltages are respectively applied, initialized based on an initial voltage applied via the fourth transistor turned on while the sixth and seventh transistors are turned on.

The driving circuit may further include an eighth transistor which is connected to and disposed between an anode terminal of the inorganic light emitting device and a cathode terminal of the inorganic light emitting device.

The eighth transistor may be configured to, before the inorganic light emitting device is mounted on the driving circuit, be turned on to check whether the driving circuit is abnormal, and after the inorganic light emitting device is mounted on the driving circuit, to be turned on to discharge an electric charge remaining in the inorganic light emitting 50 device.

In accordance with another aspect of the disclosure, a method for driving a display panel is provided. In the display panel, a plurality of pixels respectively including a plurality of sub pixels are arranged in a matrix form on a glass. Each of the plurality of sub pixels includes a driving circuit formed on the glass and configured to receive a pulse amplitude modulation (PAM) data voltage and a pulse width modulation (PWM) data voltage, and an inorganic light emitting device mounted on the driving circuit to be electrically connected to the driving circuit, and configured to emit a light based on a driving current provided from the driving circuit. The method includes compensating a threshold voltage of a driving transistor included in the driving circuit based on a driving voltage of the driving circuit, setting the applied PAM data voltage and the applied PWM data voltage, and providing, to the inorganic light emitting device, a driving current having an amplitude corresponding

to the applied PAM data voltage and a pulse width corresponding to the applied PWM data voltage. The PAM data voltage is applied at once to the plurality of pixels included in the display panel.

According to the various example embodiments, a wavelength shift of a light emitted from an inorganic light emitting device included in a display panel according to a grayscale or gradation can be prevented.

In addition, it is possible to correct a stain or color of the light emitting device included in the display panel, and even in a case that a large-area tiled display panel is configured by combining a display panel in the form of a plurality of modules, a difference of brightness or color among the respective modular display panels can be corrected.

Further, a more optimized driving circuit design is enabled so that the inorganic light emitting device can be driven more stably and efficiently, thereby contributing to a miniaturization and lightening of a display panel.

Other aspects, advantages, and salient features of the 20 disclosure will become apparent to those skilled in the art from the following detailed description, which, taken in conjunction with the annexed drawings, discloses various embodiments of the disclosure.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The above and other aspects, and advantages of certain embodiments of the disclosure will be more apparent from the following description taken in conjunction with the 30 accompanying drawings, in which:

FIG. 1 is a diagram illustrating a wavelength shift according to a magnitude of a driving current flowing through a blue LED, a green LED, and a red LED;

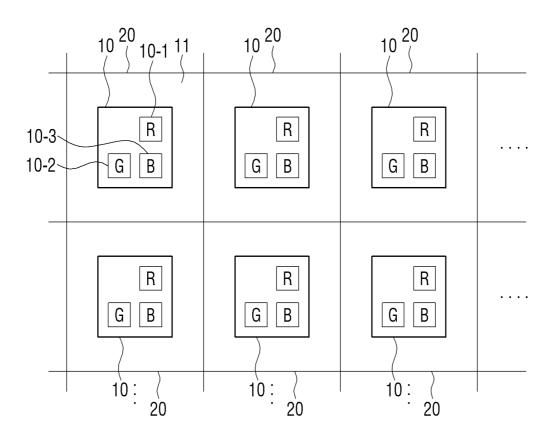

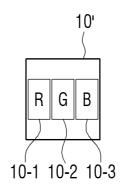

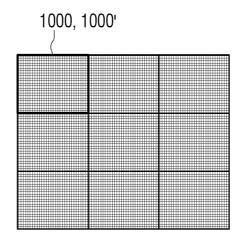

FIG. 2A is a diagram illustrating a pixel structure of a 35 display panel, according to an example embodiment;

FIG. 2B is a diagram illustrating a sub-pixel structure, according to another example embodiment;

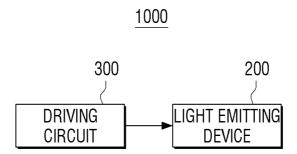

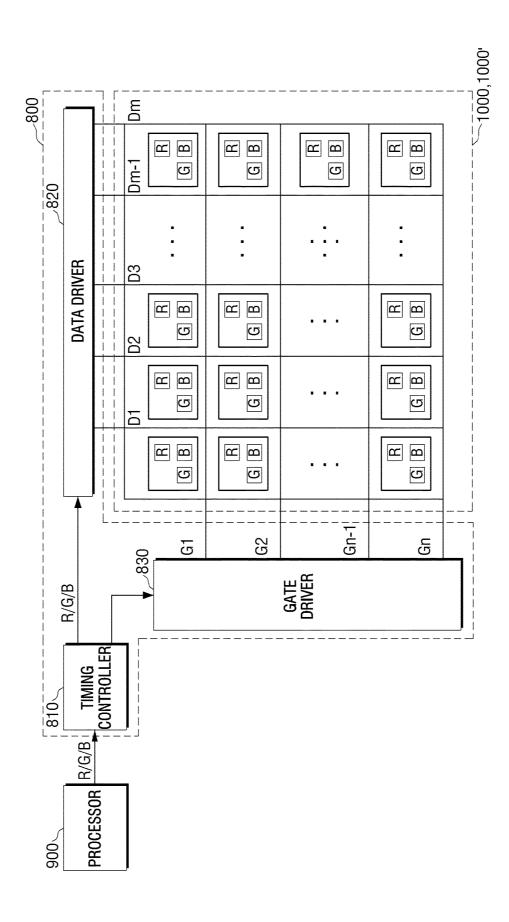

FIG. 3 is a block diagram illustrating a configuration of a display panel, according to an example embodiment;

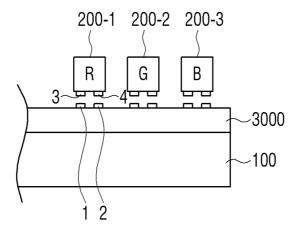

FIG. 4 is a cross-sectional view of a display panel, according to an example embodiment;

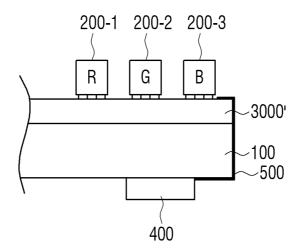

FIG. **5** is a cross-sectional view of a display panel, according to another example embodiment;

FIG. **6** is a plane view illustrating a thin film transistor 45 (TFT) layer, according to an example embodiment;

FIG. 7 is a block diagram and circuit diagram related to one sub pixel, according to an example embodiment;

FIG.  $\hat{\mathbf{8}}$  is a circuit diagram of a pulse width modulation (PWM) driving circuit, according to an example embodi- 50 ment.

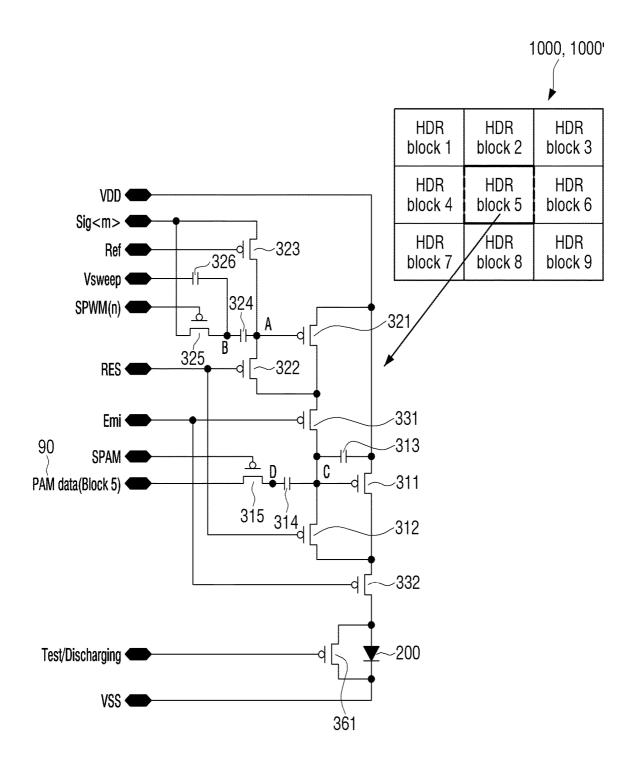

FIG. 9 is a detailed circuit diagram of a driving circuit, according to an example embodiment;

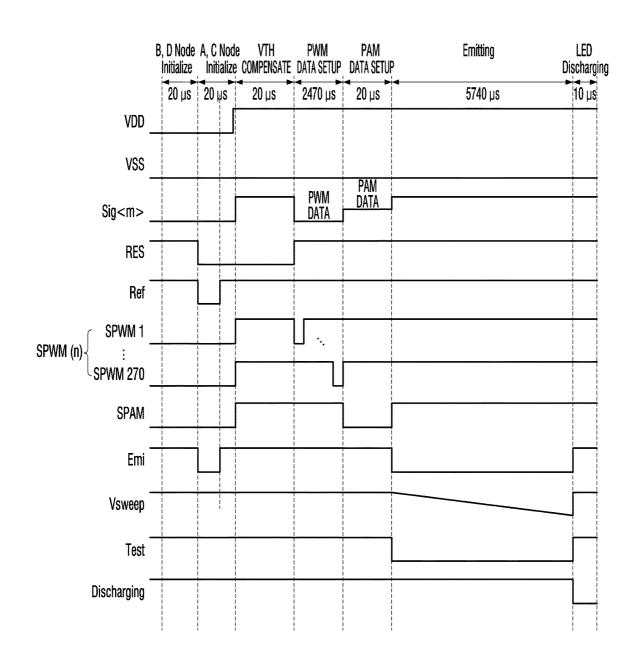

FIG. 10 is a timing diagram of various signals for driving a driving circuit of FIG. 9, according to an example embodi- 55 ment:

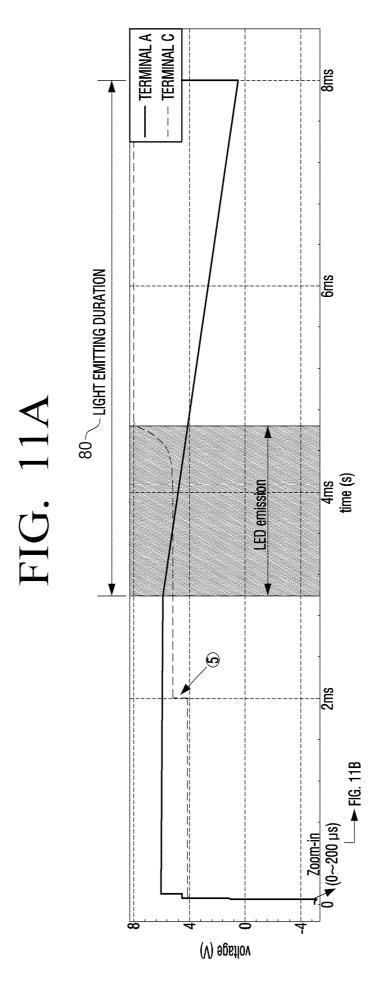

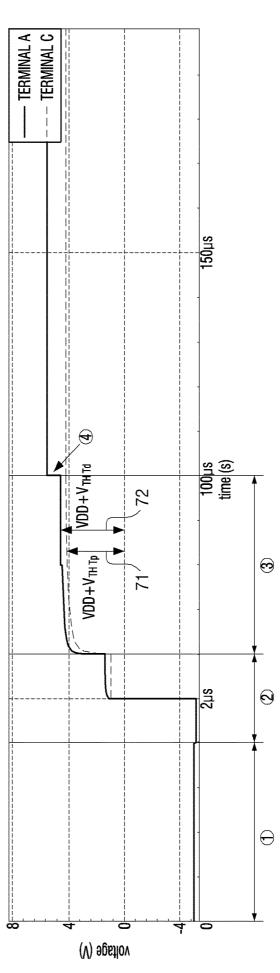

FIGS. 11A and 11B are experiment waveforms for nodes A and C of a driving circuit, according to an example embodiment:

FIGS. **12**A and **12**B are diagrams illustrating a high 60 dynamic range (HDR) realized through a display panel, according to an example embodiment;

FIG. 13 is a diagram illustrating a configuration of a display apparatus, according to an example embodiment; and

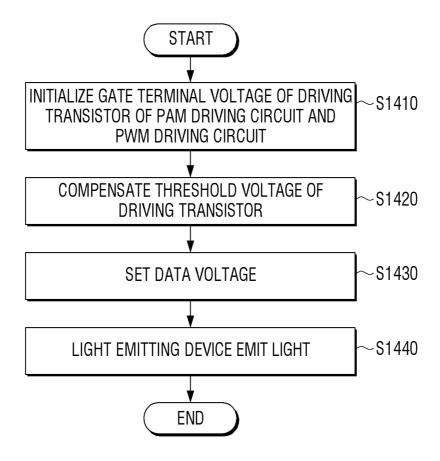

FIG. **14** is a flowchart illustrating a method for driving a display apparatus, according to an example embodiment.

6

The same reference numerals are used to represent the same elements throughout the drawings.

### DETAILED DESCRIPTION

In the following description, well-known functions or constructions are not described in detail since they would obscure the application with unnecessary detail. In addition, the overlapped description of the same element is omitted as much as possible.

The term "unit" is provided or mixed up in use for the ease of preparing the present specification, which does not itself have a distinct meaning or serve a purpose.

The terms used in the following description are provided to explain example embodiments and are not intended to limit the scope. It is to be understood that the singular forms "a," "an," and "the" include plural referents unless the context clearly dictates otherwise.

Throughout this specification, it will be understood that the term "comprise" and variations thereof, such as "comprising" and "comprises", specify the presence of features, numbers, steps, operations, components, parts, or combinations thereof, described in the specification, but do not preclude the presence or addition of one or more other features, numbers, steps, operations, components, parts, or combinations thereof.

In the description, the terms "first, second, and so forth" are used to describe diverse elements regardless of their order and/or importance and to discriminate one element from other elements, but are not limited to the corresponding elements.

If it is described that a certain element (e.g., first element) is "operatively or communicatively coupled with/to" or is "connected to" another element (e.g., second element), it should be understood that the certain element may be connected to the other element directly or through still another element (e.g., third element). Meanwhile, when it is mentioned that one element (e.g., first element) is "directly coupled" with or "directly connected to" another element (e.g., second element), it may be understood that there is no element (e.g., third element) present between the element and the other element.

Unless indicated otherwise, it is to be understood that all the terms used in the disclosure including technical and scientific terms has the same meaning as those that are understood by those who skilled in the art.

Hereinafter, the disclosure will be described in detail with reference to the accompanying drawings.

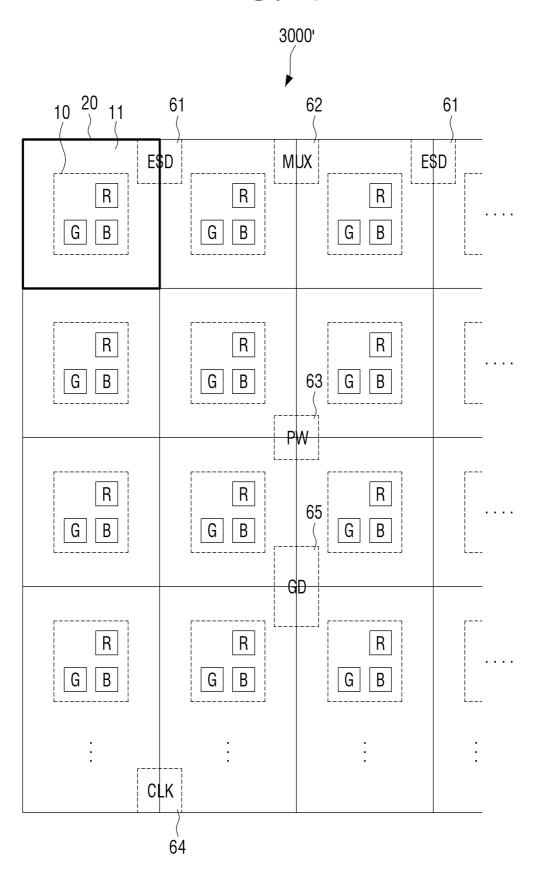

FIG. 2A is a diagram illustrating a pixel structure of a display panel 1000, according to an example embodiment. As illustrated in FIG. 2A, the display panel 1000 may include a plurality of pixels 10 which are arranged in a matrix form.

The respective pixels 10 may include a plurality of sub-pixels 10-1, 10-2 and 10-3. For example, one pixel 10 included in the display panel 1000 may include three types of sub-pixels: a red (R) sub-pixel 10-1, a green (G) sub-pixel 10-2, and a blue (B) sub-pixel 10-3. That is, one set of R, G and B sub-pixels may constitute a unit pixel of the display panel 1000.

Referring to FIG. 2A, it may be understood that one pixel area 20 of the display panel 1000 may include an area 10 occupied with pixels, and a remaining peripheral area 11.

The area 10 occupied with pixels 10 may include the R, 65 G and B sub-pixels 10-1 to 10-3. The R sub-pixel 10-1 may include an R light emitting device and a driving circuit for driving the R light emitting device. The G sub-pixel 10-2

may include a G light emitting device and a driving circuit for driving the G light emitting device. The B sub-pixel **10-3** may include a B light emitting device and a driving circuit for driving the B light emitting device.

The remaining area 11 peripheral to the pixel 10 may, as 5 will be described with reference to FIGS. 5 and 6, include various circuits for driving the driving circuit according to an example embodiment.

FIG. 2B is a diagram illustrating a sub-pixel structure, according to another example embodiment. Referring to 10 FIG. 2A, it may be understood that the sub-pixels 10-1 to 10-3 in the one pixel 10 are arranged in an L shape of which the left and right side are switched. However, the example is not limited thereto, and as illustrated in FIG. 2B, the R, G and B sub-pixels 10-1 to 10-3 may be arranged in a row 15 inside a pixel 10'. However, the disposition form of the sub-pixels is only an example, and a plurality of sub-pixels are disposed in various forms inside the respective pixels according to example embodiments.

In the example described above, a pixel includes three 20 types of sub-pixels, but is not limited thereto. For example, a pixel may be implemented of four types such as R, G, B and white (W), and according to an example embodiment, a different number of pixels may be included in one pixel. Hereinafter, an example in which the pixel 10 includes three 25 types of sub-pixels such as R, G and B will be described for convenience of explanation.

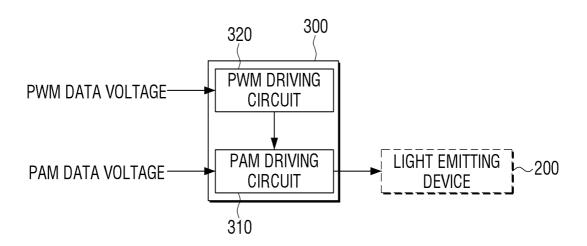

FIG. 3 is a block diagram illustrating a configuration of a display panel, according to an example embodiment. Referring to FIG. 3, the display panel 1000 may include a driving 30 circuit 300 and a light emitting device 200 (or light emitting diode). The display panel 1000 may include a driving circuit 300 disposed on a glass, and a light emitting device 200 disposed on the driving circuit 300 as will be described later.

For example, the light emitting device 200 may be 35 mounted on the driving circuit 300 so that the light emitting device 200 is electrically connected to the driving circuit 300, and may emit light on the basis of a driving current provided from the driving circuit 300.

The light emission device 200 may be included in the 40 sub-pixels 10-1 to 10-3 of the display panel 1000, and may be of a plurality of types according to a color of light. For example, the light emitting device 200 may include a red (R) light emitting device emitting light in red color, a green (G) light emitting device emitting light in green light, and a blue 45 (B) light emitting device emitting light in blue color.

Accordingly, a type of sub-pixel may be determined according to a type of the light emitting device 200 included in the sub-pixel. That is, the R light emitting device may be included in the R sub-pixel 10-1. The G light emitting device 50 may be included in the G sub-pixel 10-2. The B light emitting device may be included in the B sub-pixel 10-3.

The light emitting device **200** may be an inorganic light emitting device (or inorganic light emitting diode) by means of an inorganic material which is different from an organic 55 light emitting device (OLED)(or organic light emitting diode) fabricated using an organic material. Hereinafter, the LED refers to an inorganic light emitting device which is distinguished from the OLED.

According to an example embodiment, the light emitting 60 device 200 may be a micro light emitting diode (micro-LED). The micro LED refers to a subminiature inorganic light emitting device having a size of less than or equal to 100 micrometers (µm) self-illuminating without a backlight or a color filter.

In addition, the light emitting device 200 may emit light according to a driving current provided by the driving circuit

8

**300.** For example, the light emitting device **200** may emit light with different brightnesses according to an amplitude or a pulse width of a driving current provided from the driving circuit **300**. Here, the pulse width of the driving current may be expressed as a duty ratio of the driving current or a driving time of the driving current.

For example, the light emitting device 200 may emit light of a higher brightness with the increase in the amplitude of the driving current and with the increase in the pulse width (that is, with the increase in the duty ratio or with the increase in the driving time). However, the example is not limited thereto.

The driving circuit 300 may drive the light emitting device 200. For example, the driving circuit 300 may pulse amplitude modulation (PAM) drive or pulse width modulation (PWM) drive the light emitting device 200 to control a grayscale or gradation of a light emitted by the light emitting device 200.

That is, the driving circuit 300 may, for example, receive application of a PAM data voltage and a PWM data voltage from a data driver (not illustrated) and control an amplitude and pulse width of a driving current driving the light emitting device 200 together, and provide the driving current of which amplitude and pulse width are controlled together to the light emitting device 200, and drive the light emitting device 200.

Here, the amplitude and the pulse width of the driving current being controlled "together" does not mean that the driving circuit 300 controls the amplitude and the pulse width of the driving current simultaneously in time, but means that the PAM drive method and the PWM drive method are employed together to express a grayscale or gradation.

The driving circuit 300 may control a pulse width of a driving current having an amplitude corresponding to the applied PAM data voltage on the basis of the applied PWM data voltage.

According to an example embodiment, the driving circuit 300 may compensate a deviation between driving circuits included in each of a plurality of sub pixels based on a driving voltage (VDD) driving the driving circuit 300.

In addition, the PAM data voltage may be applied at once to all pixels (or all sub pixels) included in the display panel **1000**. A specific description regarding this operation will be explained below.

According to an example embodiment, the driving circuit 300 may drive the light emitting device 200 and express a grayscale or gradation by the sub pixel. As described above, the display panel 1000 may include sub-pixels by the light emitting device 200, and thus, unlike a liquid crystal display (LCD) panel using a plurality of LEDs emitting light in a single color as a backlight, the driving circuit 300 may drive the light emitting device 200 and differently expresses a grayscale or gradation by the sub-pixel.

To this end, the respective sub-pixels included in the display panel 1000 may include the light emitting device 200 and a driving circuit 300 for driving the corresponding light emitting device 200. That is, the driving circuit 300 for driving the respective device 200 may be present for each sub-pixel.

The PWM drive method is a method of expressing a grayscale or gradation according to a duration of light emission of the light emitting device 200. Accordingly, in a case that the light emitting device 200 is driven using the PWM method, even if the driving current has the same amplitude, it is possible to express various grayscales or gradations by adjusting the pulse width of the driving

current and controlling the duration of light emission of the light emitting device 200. Accordingly, it is possible to solve the problem of a wavelength shift of light emitted by an LED (in particular, micro-LED) by driving the LED solely by the PAM method.

To this end, the driving circuit 300 may include a PAM driving circuit and a PWM driving circuit for each sub pixel, and this will be described in greater detail below.

FIG. 4 is a cross-sectional view of a display panel 1000, according to an example embodiment. With reference to 10 FIG. 4, only one pixel included in the display panel 1000 is described for convenience of explanation.

Referring to FIG. 4, the display panel 1000 may include a glass 100, a thin film transistor (TFT) layer 3000, and light emitting devices R, G and B 200-1, 200-2 and 200-3. The 15 driving circuit 300 (not illustrated) may be implemented as a thin film transistor (TFT) and included in the TFT layer 3000 disposed on the glass 100. The respective light emitting devices R, G and B 200-1 to 200-3 may be arranged on the TFT layer 3000 and included in the respective sub pixels 20 10-1 to 10-3 of the display panel 1000.

As described above, the display panel 1000 in which the TFT layer 3000 and the light emitting devices 200-1 to 200-3 are disposed on the glass 100 may be referred to as a display panel of a chip on glass (COG) type. The display 25 implemented as TFTs, and may be formed on a first surface panel of the COG type is different from a display panel of a chip on board (COB) type in which a TFT layer and a light emitting device layer are disposed on a substrate such as a synthetic resin and the like.

In this case, the TFT layer 3000 may be a low temperature 30 poly silicon (LTPS) TFT, but is not limited thereto. Meanwhile, the TFT layer 3000 disposed on the glass 100 and the glass 100 may be added together and referred to as a TFT panel or a glass substrate. A type or characteristic of the glass 100 included in the glass substrate is not related to the 35 example embodiments so that an explanation thereof is omitted.

Although not expressly illustrated in the drawings, the driving circuit 300 for driving the respective light emitting devices 200-1 to 200-3 may be present on the TFT layer 40 3000 for each of the light emitting devices 200-1 to 200-3. The light emitting devices R, G and B 200-1 to 200-3 may be arranged on the TFT layer 3000 so that they are respectively electrically connected to the corresponding driving circuit 300.

For example, as illustrated in FIG. 4, the R light emitting device 200-1 may be mounted or arranged so that an anode electrode 3 and a cathode electrode 4 of the R light emitting device 200-1 are respectively connected to an anode electrode 1 and a cathode electrode 2 disposed on the driving 50 circuit 300 (not illustrated) for driving the R light emitting device 200-1, and the same applies to the G light emitting device 200-2 and the B light emitting device 200-3. According to an example embodiment, any one of the anode electrode 1 and the cathode electrode 2 may be implemented 55 as a common electrode.

With reference to FIG. 4, an example in which the light emitting device 200-1 to 200-3 is a micro-LED of a flip chip type is described. However, the example is not limited thereto, and according to an example embodiment, the light 60 emitting device 200-1 to 200-3 may be a micro-LED of a lateral type or a micro-LED of a vertical type.

According to an example embodiment, the display panel 1000 may further include a multiplexer (MUX) circuit for selecting any one of the plurality of sub pixels 10-1 to 10-3 65 included in the pixel 10, an electro static discharge (ESD) circuit for preventing a static electricity occurring on the

10

display panel 1000, a power circuit for supplying power to the driving circuit 300, a clock provision circuit for providing a clock driving the driving circuit 300, at least one gate driver for driving pixels of the display panel 1000 arranged in a matrix form by the horizontal line (or by the row), a data driver (or a source driver) for providing a data voltage (for example, a PAM data voltage, a PWM data voltage, or the like) to the respective pixels or to the respective sub-pixels, and the like.

An example display panel further comprising these various circuits will be described in greater detail below with reference to FIGS. 5 and 6. In FIGS. 5 and 6, the same elements described above will not be described in detail.

FIG. 5 is a cross-sectional view of a display panel 1000', according to an example embodiment. As illustrated in FIG. 5, the display panel 1000' may include a TFT layer 3000' including a driving circuit 300 (not illustrated) disposed on the glass 100, a light emitting device 200-1 to 200-3 disposed on the TFT layer 3000' and respectively included in a sub pixel of the display panel 1000', the various circuits 400 for driving the driving circuit 300, and a connection cable 500 electrically connecting the TFT layer 3000' with the various circuits 400.

The TFT layer 3000' may include a driving circuit 300 of the glass 100.

The various circuits 400 may include a MUX circuit for operation of the driving circuit 300, an electro static discharge (ESD) circuit, a power circuit, a clock provision circuit, a gate driver, a data driver, and etc., and may be disposed or arranged on a second surface of the glass 100.

According to an example embodiment, the display panel 1000' may include the connection cable 500 disposed in an edge area of a TFT substrate, and electrically connecting the TFT layer 3000' disposed on a first surface of the glass 100 with the various circuits 400 disposed on a second surface of the glass 100.

The connection cable 500 is disposed in the edge area of the TFT substrate because otherwise, a crack may occur on the glass due to a difference of temperature between a fabrication process of a TFT substrate and a process of filling a hole with conductive materials, where a hole penetrating the glass 100 is disposed and circuits arranged on the opposite sides of the glass 100 are connected to each other,

In the example described above, all circuits for operation of the driving circuit 300 are, as in the reference numeral 400, separately disposed on the opposite side of the glass 100 surface on which the TFT layer 3000' is disposed. However, the example is not limited thereto. That is, all or some of the various circuits described above may be disposed on the TFT layer 3000'.

For example, all the various circuits described above may be disposed on the TFT layer 3000'. In this case, it is not necessary that a circuit is additionally arranged on the other surface of the glass 100 and accordingly, the connection cable 500 of FIG. 5 connecting front and rear surfaces of the glass 100 would not be necessary, either.

As another example, the MUX circuit, the ESD circuit, the power circuit, the clock provision circuit, and the gate driver may be implemented as TFTs and included in the TFT layer 3000', and the display panel may be implemented in such a way that the data driver circuit is additionally arranged on the other side of the glass 100. FIG. 6 is a diagram provided to explain such an example embodiment.

FIG. 6 is a cross-sectional view of a TFT layer 3000', according to an example embodiment. In detail, FIG. 6

illustrates a disposition of various circuits included in the TFT layer 3000' of the display panel 1000'.

Referring to FIG. 6, an entire pixel area 20 occupied by (or corresponding to) one pixel in the TFT layer 3000' may include an area 10 in which various driving circuits 300 for 5 driving the R, G and B sub pixels are arranged, and a peripheral remaining area 11.

According to an example embodiment, a size of the area 10 occupied by a driving circuit 300 for the respective R, G and B sub pixels may be, for example, a size of about a 10 quarter of the entire pixel area 20, but is not limited thereto.

As described above, one pixel area 20 may include the remaining area 11 in addition to the area 10 occupied by the driving circuit 300 for driving the respective sub pixels, and so may the other pixels.

That is, according to an example embodiment, many spaces other than an area occupied with the driving circuit 300 are present in the TFT layer 3000', and thus, the ESD circuit 61, the MUX circuit 62, the power circuit 63, the clock provision circuit **64**, and the gate driver circuit **65** may 20 be implemented as TFTs and included in the remaining area 11 of the TFT layer 3000' as illustrated in FIG. 6. In this case, the data driver circuit may be arranged on the other surface of the glass 100 as in the reference numeral 400 of FIG. 5.

tive ESD circuit 61, the MUX circuit 62, the power circuit 63, the clock provision circuit 64, and the gate driver circuit **65** is only a non-limiting example.

In addition, an example embodiment in which various circuits are arranged on both sides as being divided based on 30 the glass 100 is not limited to the example illustrated in FIG. 6, and at least one circuit from among the ESD circuit 61, the MUX circuit 62, the power circuit 63, the clock provision circuit 64, and the gate driver circuit 65 of FIG. 6 may be arranged on the other surface of the glass 100 as in the 35 reference numeral 400.

A constitution and operation of the driving circuit 300 according to various example embodiments will be described in detail with reference to FIGS. 7, 8, 9, 10, 11A

FIG. 7 is a block diagram related to one sub pixel, according to an example embodiment. That is, FIG. 7 illustrates only one light emitting device 200, and a driving circuit 300 for driving the one light emitting device 200. Accordingly, the light emitting device 200 and the driving 45 circuit 300 as illustrated in FIG. 7 may be provided in the display panel 1000 and 1000' by the sub pixel. Meanwhile, the light emitting device 200 may be a micro-LED in any one color from among R, G and B.

As described above, the driving circuit 300 may receive 50 application of a PAM data voltage and a PWM data voltage, and control an amplitude and a pulse width of a driving current driving the light emitting device 200. To this end, the driving circuit 300 may include a PAM driving circuit 310 and a PWM driving circuit 320 as illustrated in FIG. 7.

The driving circuit 300 may be provided for each sub pixel, and one driving circuit 300 drives one sub pixel and thus may be referred to as a pixel circuit depending on circumstances. In this case, the PAM driving circuit 310 may be referred to as a PAM pixel circuit, and the PWM driving 60 circuit 320 may be referred to as a PWM pixel circuit. For convenience of explanation, the terms "driving circuit" "PWM driving circuit" and "PWM driving circuit 320" are used to describe an example embodiment.

Referring to FIG. 9, the PAM driving circuit 310 may 65 include a first driving transistor 311, and control an amplitude of a driving current provided to the light emitting

12

device 200 based on the applied PAM data voltage. The PWM driving circuit 320 may include a second driving transistor 321, and control a pulse width of a driving current provided to the light emitting device 200 based on the applied PWM data voltage.

The first driving transistor 311 may provide a driving current of different amplitudes to the light emitting device 200 according to a magnitude of voltage applied to a gate terminal C. Accordingly, the PAM driving circuit 310 may provide a driving current having an amplitude corresponding to the applied PAM data voltage to the light emitting device 200 via the first driving transistor 311.

The second driving transistor 321 may be connected to the  $_{15}\,$  gate terminal C of the first driving transistor 311, and control a gate terminal voltage of the first driving transistor 311, thereby controlling a pulse width of a driving current.

For example, after the light emitting device 200 starts light emission according to a driving current provided by the first driving transistor 311, when a duration corresponding to a PWM data voltage has elapsed, the second driving transistor 321 may turn off the first driving transistor 311 and control a pulse width of the driving current.

Accordingly, the PWM driving circuit 320 may control a Meanwhile, the location, size and number of the respec- 25 duration of a driving current (that is, a driving current having an amplitude corresponding to the PAM data voltage) provided to the light emitting device 200 by the PAM driving current on the basis of the PWM data voltage, and thereby a pulse width of the driving current can be controlled.

> The light emitting device 200 may emit light according to a driving current provided by the driving circuit 300. For example, the light emitting device 200 may emit light with different brightnesses according to an amplitude or a pulse width of a driving current provided from the driving circuit 300. Here, the pulse width of the driving current may be expressed as a duty ratio of the driving current or a driving time of the driving current.

> For example, the light emitting device 200 may emit light having a higher brightness with the increase in the amplitude of the driving current and with the increase in the pulse width (that is, with the increase in the duty ratio or with the increase in the driving time). However, the example is not limited thereto.

According to an example embodiment, the driving circuit 300 may compensate a deviation between driving circuits included in each of a plurality of sub pixels based on a driving voltage (VDD) driving the driving circuit 300.

For example, a plurality of sub pixels are present in the display panel 1000 and 1000', and the respective sub pixels may include the corresponding first driving transistor 311. Theoretically, a transistor fabricated under the same condition has the same threshold voltage. However, actual transistors may have different threshold voltages even if they are fabricated under the same condition, and so may the first 55 driving transistors 311 included in the display panel 1000 and 1000'.

As described above, in a case that the first driving transistors 311 corresponding to the respective sub pixels have different threshold voltages, the first driving transistors 311 may apply a driving current of different amplitudes corresponding to a difference of threshold voltages to the respective light emitting devices 200 even if the same PAM data voltage is applied to the gate terminal, and this may be displayed as a stain on the image and the like. Accordingly, it is necessary to compensate a deviation of threshold voltage between the first driving transistors 311 included in the display panel 1000 and 1000'.

Meanwhile, a deviation of threshold voltage is present in the second driving transistors 321 present for each sub pixel of the display panel 1000 and 1000', and if the deviation is not compensated, even if the same PWM data voltage is applied to the second driving transistors 321, a driving 5 current of different pulse widths corresponding to the deviation of threshold voltage is provided to the respective light emitting device 200, which is a problem. This is described with regard to the PAM driving circuit 310 above. Accordingly, it is necessary to compensate a deviation of threshold 10 voltage between the second driving transistors 321 included in the display panel 1000 and 1000' as well.

The deviation between the driving circuits described above may be a deviation of threshold voltage between the first driving circuits and a deviation of threshold voltage 15 between the second driving circuits respectively corresponding to a plurality of sub pixels of the display panel **1000**.

For example, when the driving voltage (VDD) is applied, the PAM driving circuit 310 may apply, to a gate terminal C of the first driving transistor 311, a voltage (hereinafter 20 referred to as "first voltage") based on the driving voltage (VDD) and the threshold voltage of the first driving transistor 311. Accordingly, the first driving transistor 311 may, regardless of the threshold voltage of the first driving transistor 311, provide, to the light emitting device 200, a 25 driving current having an amplitude corresponding to a magnitude of a PAM data voltage to be applied later.

When the driving voltage (VDD) is applied, the PWM driving circuit 320 may apply, to a gate terminal A of the second driving transistor 321, a voltage (hereinafter referred 30 and a sot to as "second voltage") based on the driving voltage (VDD) and the threshold voltage of the second driving transistor 321 may, regardless of the threshold voltage of the first driving transistor 321, provide, to the light emitting device 200, a 35 driving current having a pulse width corresponding to a magnitude corresponding to a PAM data voltage to be applied later.

Accordingly, it is possible to solve a problem caused by a deviation between driving circuits included in the display 40 panel 1000 and 1000'.

According to an example embodiment, when after a first voltage is applied to the gate terminal C of the first driving transistor 311 and a second voltage is applied to the gate terminal A of the second driving transistor 321 as described 45 above, when a PAM data voltage and a PWM data voltage are applied, the driving circuit 300 may provide, to the light emitting device 200, a driving current of amplitude corresponding to the applied PAM data voltage and of a pulse width corresponding to the applied PWM data voltage.

For example, in a state that the first voltage is applied to the gate terminal C of the first driving transistor 311, when the PAM data voltage is applied, the PAM driving circuit 310 may apply a voltage (hereinafter referred to as "third voltage") based on the first voltage and the applied PAM data 55 voltage to the gate terminal C of the first driving transistor 311.

In addition, in a state that the second voltage is applied to the gate terminal A of the second driving transistor 321, when the PWM data voltage is applied, the PWM driving 60 circuit 320 may apply a voltage (hereinafter referred to as "fourth voltage") based on the second voltage and the applied PWM data voltage to the gate terminal A of the second driving transistor 321.

Accordingly, in a state that the third voltage is applied to 65 the gate terminal C of the first driving transistor **311** and the fourth voltage is applied to the gate terminal A of the second

14

driving transistor 321, when a driving voltage (VDD) is applied to the light emitting device 200, the PAM driving circuit 310 may provide a driving current source of an amplitude corresponding to the PAM driving voltage to the light emitting device 200, and the light emitting device 200 starts emitting light.

In this case, a sweep signal (linear shift voltage) may be applied to the PWM driving circuit 320, and the second driving transistor 321 in an off state may remain in the off state until a voltage of the gate terminal A is linearly shifted from the fourth voltage to the second voltage according to the sweep signal.

When the voltage of the gate terminal A of the second driving transistor 321 reaches the second voltage, the second driving transistor 321 may be turned on, and the driving voltage (VDD) applied to the source terminal of the second driving transistor 321 may be accordingly applied to the gate terminal C of the first driving transistor 311 via the drain terminal.

The driving voltage (VDD) is applied to the source terminal of the first driving transistor 311. Thus, when the driving voltage (VDD) is applied to the gate terminal C of the first driving transistor 311, a voltage between the gate terminal and the source terminal of the first driving transistor 311 may exceed the threshold voltage of the first driving transistor 311 and the first driving transistor 311 may be turned off. For reference, a threshold voltage of a PMOSFET has a negative value. When a voltage less than or equal to the threshold voltage is applied to in between a gate terminal and a source terminal of the PMOSFET, the PMOSFET is turned off. When a voltage greater than the threshold voltage is applied, the PMOSFET is turned off. When the first driving transistor 311 is turned off, the driving current may no longer flow, and the light emitting device 200 stops light emission.

As described above, the PWM driving circuit 320 may control the voltage of the gate terminal A of the first driving transistor 311 and control a pulse width of the driving current.

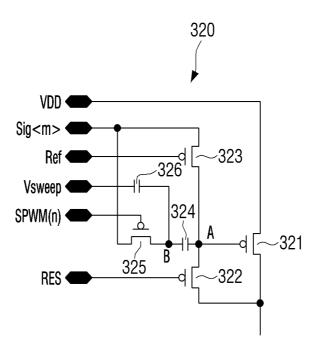

The following will explain the operation regarding a threshold voltage compensation of the second driving transistor 321 in detail by referring to FIG. 8. FIG. 8 is a circuit diagram of a pulse width modulation (PWM) driving circuit 320, according to an example embodiment. Numerical values of the various voltages described below are only an example, and the example is not limited to the corresponding values.

Referring to FIG. 8, the PWM driving circuit 320 may include a third transistor 322 connected to and disposed between a drain terminal and a gate terminal of the second driving transistor 321, a fourth transistor 323 including a drain terminal commonly connected to the gate terminal A of the second driving transistor 321 and the source terminal of the third transistor 322, a third capacitor 324 including a first terminal commonly connected to the gate terminal A of the second driving transistor 321, the source terminal of the third transistor 322 and the drain terminal of the fourth transistor 323, a fifth transistor 325 including a source terminal via which a PWM data voltage is applied, and a drain terminal connected to a second terminal B of the third capacitor 324, and a fourth capacitor 326 including a first terminal commonly connected to a second terminal of the third capacitor 324 and the drain terminal of the fifth transistor 325, and a second terminal receiving a linearlyshifting sweep signal.

As described above, when the driving voltage (VDD) is applied to the PWM driving circuit **320**, the PWM driving

circuit 320 may apply a voltage corresponding to the sum of the driving voltage (VDD) and a threshold voltage of the second driving transistor 321, that is, the second voltage, to the gate terminal A of the second driving transistor 321, and compensate the threshold voltage of the second driving transistor 321

First, the PWM driving circuit 320 may initialize each of the node B and the node A. For example, the PWM driving circuit 320 may receive input of an initial voltage (for example, -5V) from a data line (Sig<m>) via the fifth transistor 325 turned on according to a control signal SPWM (n) and apply the received initial voltage input to the node B, and receive input of an input voltage (for example, -5V) from the data line (Sig<m>) via the fourth transistor 323 turned on according to a control signal Ref and apply the received initial voltage input to the node A.

Then, the driving voltage (VDD) (for example, +8V) may be input to the source terminal of the second driving transistor 321 via a driving voltage terminal. In this case, the  $_{20}$  third transistor 322 is in a turn-on state according to a control signal RES, and the second driving transistor 321 has a gate terminal A voltage of -5V which is a low state, and thus may be fully turned on.

Accordingly, the input driving voltage (VDD) is applied 25 to the gate terminal A of the second driving transistor 321 while sequentially going through the second driving transistor 321 and the third transistor 322. However, in this case, the voltage of the gate terminal A of the second driving transistor 321 may rise up to only a voltage corresponding 30 to the sum of the driving voltage and the threshold voltage of the second driving transistor 321 rather than rising up to the input driving voltage (VDD).

When the driving voltage (VDD) is first applied via the source terminal of the second driving transistor 321, a 35 voltage of the gate terminal A of the second driving transistor 321 is in a low state (for example, -5V) and the second driving transistor 321 is fully turned on, and thus a sufficient current flows and the gate terminal A voltage of the second driving transistor 321 smoothly rises. However, a difference 40 of voltage between the gate terminal and the source terminal of the second driving transistor 321 is reduced with the increase of the gate terminal A voltage of the second driving transistor 321, and thus a current flow decreases, and as a result, when the difference of voltage between the gate 45 terminal and source terminal of the second driving transistor 321 reaches the threshold voltage of the second driving transistor 321, the second driving transistor 321 is turned off and the current flow is stopped.

That is, the driving voltage (VDD) is applied to the source 50 terminal of the second driving transistor 321, and thus the voltage of the gate terminal A of the second driving transistor 321 may rise only up to a voltage (that is, the second voltage) corresponding to the sum of the driving voltage (VDD) and the threshold voltage of the second driving 55 transistor 321. As described above, the second voltage is applied to the gate terminal A of the second driving transistor 321, thereby compensating the threshold voltage of the second driving transistor 321.

Meanwhile, the structure and operation of the PAM 60 driving circuit 310 regarding compensation of threshold voltage of the first driving transistor 311 are similar to the description regarding compensation of threshold voltage of the second driving transistor 321 described above. Thus, the structure and operation of the PAM driving circuit 310 65 regarding compensation of threshold voltage of the first driving transistor 311 would have been easily understood

16

through the circuit diagram illustrated in FIG. 9 and the timing diagram of FIG. 10, and thus the overlapping description will be omitted herein.

As described above, according to an example embodiment, a threshold voltage of the second driving transistor 321 included in the respective sub pixels of the display panel 1000 and 1000' may be internally compensated, and so may a threshold voltage of the first driving transistor 311.

Here, the term "internal compensation" means that threshold voltages of the first and second driving transistors 311

and 321 are autonomously compensated within the driving

circuit 300 while the driving circuit 300 is operated due to

a connection structure of the devices as illustrated in FIG. 8,

and this internal compensation method is distinct from an

external compensation method to compensate threshold

voltages of the first and second driving transistors 311 and

321 by correcting a data voltage itself to be applied from

outside of the driving circuit 300 to the driving circuit 300.

As described above, according to an example embodiment, the threshold voltages of the driving transistors 311 and 321 included in the display panel 1000 and 1000' are internally compensated and thus, when applying or setting a PAM data voltage to all pixels (or all sub pixels) of the display panel 1000 and 1000' to display one image frame, the PAM data voltage may be applied at once to all the pixels (or all the sub pixels) included in the display panel 1000 and 1000'. Accordingly, it is possible to secure a sufficient light emitting interval for the light emitting device 200 to emit light from among the entire time interval for displaying one image frame.

This is a distinct feature from an external compensation method in which it is necessary to sequentially scan the pixels included in the display panel 1000 and 1000' for each line and separately apply the PAM data voltage for which the threshold voltage has been compensated for each line.

According to the example embodiment described above, the PWM data voltage may be sequentially applied to the pixels included in the display panel 1000 and 1000' for each line to express a grayscale or gradation for each line.

The following will explain the details and operation of the driving circuit 300 in detail by referring to FIGS. 9 and 10.

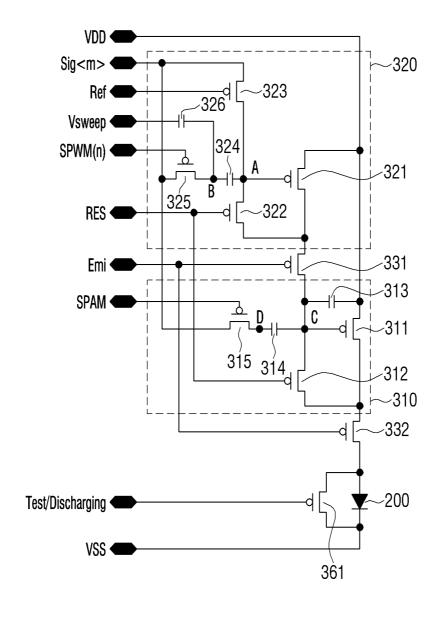

FIG. 9 is a detailed circuit diagram of a driving circuit 300, according to an example embodiment. The devices included in the driving circuit 300 and a connection relationship between the devices will be first described with reference to FIG. 9.

FIG. 9 illustrates one sub pixel-related circuit, that is, one light emitting device 200, and a driving circuit 300 for driving the light emitting device 200. Accordingly, the light emitting device 200 and the driving circuit 300 as illustrated in FIGS. 7A and 7B may be provided in the display panel 1000 and 1000' by the sub pixel. Meanwhile, the light emitting device 200 may be an LED in any one color from among R, G and B.

Referring to FIG. 9, the driving circuit 300 may include a PAM driving circuit 310, a PWM driving circuit 320, sixth to eighth transistors 331, 332 and 361.

The PAM driving circuit 310 may include a first transistor 312 which is connected to and disposed between the drain terminal and the gate terminal of the first driving transistor 311, a first capacitor 313 including a first terminal commonly connected to the source terminal of the first driving transistor 311, the source terminal of the second driving transistor 321 and the driving voltage (VDD) terminal of the driving circuit 300, a second capacitor 314 including a first terminal commonly connected to the gate terminal C of the first driving transistor 311, a second terminal of the first

capacitor 313 and the source terminal of the first transistor 312, and a second transistor 315 including a source terminal via which a data signal (Sig<m>) is applied, and a drain terminal connected to the second terminal D of the second capacitor 314.

While the first transistor 312 is turned on according to a control signal RES, when the driving voltage (VDD) is applied to the PAM driving circuit 310 by the driving voltage (VDD) terminal via the source terminal of the first driving transistor 311, the PAM driving circuit 310 may 10 apply a first voltage corresponding to the driving voltage (VDD) and the threshold voltage of the first driving transistor 311 to the gate terminal C of the first driving transistor 311 via the turned-on driving transistor 311.

In addition, when the PAM data voltage is applied via the 15 source terminal of the second transistor 315, the PAM driving circuit 310 may apply a third voltage corresponding to the sum of the first voltage and the applied PAM data voltage to the gate terminal C of the first driving transistor 311. A voltage corresponding to the sum of the applied PAM 20 data voltage and the threshold voltage of the first driving transistor 311 may be charged in the opposite terminals of the first capacitor 313.

The PWM driving circuit 320 may, as described above, include the third transistor 322 connected to and disposed 25 between the drain terminal and the gate terminal of the second driving transistor 321, the fourth transistor 323 including a drain terminal commonly connected to the gate terminal A of the second driving transistor 321 and the source terminal of the third transistor 322, the third capacitor 324 including a first terminal commonly connected to the gate terminal A of the second driving transistor 321, the source terminal of the third transistor 322 and the drain terminal of the fourth transistor 323, the fifth transistor 325 including a source terminal via which a data voltage 35 (Sig<m>) is applied, and a drain terminal connected to the second terminal B of the third capacitor 324, and the fourth capacitor 326 including a first terminal commonly connected to a second terminal of the third capacitor 324 and the drain terminal of the fifth transistor 325, and a second terminal 40 receiving a linearly-shifting sweep signal.

While the third transistor 322 is turned on, when the driving voltage (VDD) is applied to the PWM driving circuit 320 by the driving voltage terminal via the source terminal of the second driving transistor 321, the PWM driving 45 circuit 320 may apply a second voltage corresponding to the driving voltage (VDD) and the threshold voltage of the second driving transistor 321 to the gate terminal A of the second driving transistor 321 via the turned-on driving transistor 321.

In addition, when the PWM data voltage is applied to the PWM driving circuit 320 via the source terminal of the fifth transistor 325, the PWM driving circuit 320 may apply a fourth voltage corresponding to the sum of the second voltage and the applied PWM data voltage to the gate 55 terminal of the second transistor 321.

The sixth transistor 331 may include a source terminal which is commonly connected to the drain terminal of the second driving transistor 321 and the drain terminal of the third transistor 322, and a drain terminal which is commonly 60 connected to the gate terminal C of the first driving transistor 311, the second terminal of the first capacitor 313, the first terminal of the second capacitor 314, and the source terminal of the first transistor 312. The sixth transistor 331 may be turned on or off according to the control signal Emi, and 65 electrically connect the PAM driving circuit 310 and the PWM driving circuit 320 or separate them from each other.

18

The seventh transistor 332 may include a source terminal commonly connected to the drain terminal of the first driving transistor 311 and the drain terminal of the first transistor 312, and a drain terminal connected to an anode terminal of the light emitting device 200. The seventh transistor 332 may be turned on or off according to the control signal Emi, and electrically connect the PAM driving circuit 310 and the light emitting device 200 or separate them from each other.

The eighth transistor 361 may be connected to and disposed between the anode terminal and cathode terminal of the light emitting device 200. Before the light emitting device 200 is mounted on the TFT layer 3000 and electrically connected to the driving circuit 300, the eighth transistor 361 may be turned on according to the control signal Test to check the abnormality of the driving circuit 300, and after the light emitting device 200 is mounted on the TFT layer 3000 and electrically connected to the driving circuit 300, the eighth transistor 361 may be turned on according to a control signal (Discharging) to discharge the charge remaining in the light emitting device 200.

Meanwhile, the cathode terminal of the light emitting device 200 may be connected to a ground voltage (VSS) terminal.

The following will explain the operation of the driving circuit 300 in detail by referring to FIG. 10. FIG. 10 is a timing diagram of various signals for driving a driving circuit of FIG. 9, according to an example embodiment. Numerical values of the various voltages and times described below are only an example, and the example is not limited to the corresponding values. In addition, the name of the respective durations is not limited to the illustration of FIG. 10.

Referring to FIG. 10, the driving circuit 300 may be, to display one image frame, driven in the order of a node initialization duration (Initialize), a threshold voltage (Vth) compensation duration, a data voltage setup duration, a light emitting duration (Emitting), and a discharge duration (LED Discharging).

The initialization duration may include an initialization duration of nodes B and D and an initialization duration of nodes A and C.

The initialization duration is a duration for initializing voltages of the second terminal of the third capacitor 324 (that is, the node B) and the second terminal of the second capacitor 315 (that is, the node D) to stabilize voltages of the second and first driving transistors 321 and 311 (that is, the node A and the node B).

The driving circuit 300 may initialize the voltages of the B and D terminals to the initial voltage (for example, -5V) during the initialization duration of the nodes B and D. For example, the fifth transistor 325 and the second transistor 315 are turned on according to the control signals SPWM(n) and SPAM during the initialization duration of the nodes B and D, and thus an initial voltage (for example, -5V) applied by the data signal line (Sig<m>) may be applied to the node B via the fifth transistor 325, and applied to the node B via the second transistor 315.

The initialization duration of nodes A and C is a duration for initializing voltages of the gate terminal of the second driving transistor **321** (that is, the node A) and the gate terminal of the first driving transistor **311** (that is, the node C).

During the initialization duration of nodes A and C, the control signals RES, Ref and Emi as well as the control signals SPWM(n) and SPAM have a low voltage (for example, -5V). In addition, a low voltage (for example,

-5V) may be applied to the driving voltage (VDD) terminal and the ground voltage (VSS).

Accordingly, the initial voltage (for example, -5V) applied by the data signal line (Sig<m>) may be applied to the node A via the fourth transistor 323 turned on according to the control signal Ref, and applied to the node C via the third transistor 322 turned on according to the control signal RES and the sixth transistor 331 turned on according to the control signal Emi.

The initial voltage (for example, -5V) is applied to the 10 anode terminal of the light emitting device **200** via the first transistor **312** turned on according to the control signal RES and the seventh transistor **332** turned on according to the control signal Emi, and thus -5V may be applied to each of the opposite terminals of the light emitting device **200** and 15 the light emitting device **200** may not emit light.

Meanwhile, during the initialization duration of the nodes A and C, a voltage of the driving voltage (VDD) terminal rises from a low voltage (–5V) to the driving voltage (VDD, for example, +8V) because it is necessary to apply the 20 driving voltage (VDD) to the driving voltage (VDD) terminal to enable the light emitting device **200** to emit light.

A voltage of the driving voltage terminal is raised immediately after the nodes A and C are initialized as illustrated in FIG. **10** rather than during the data voltage setup/threshold voltage (Vth) compensation duration or light emitting duration (Emitting) because it is more stable to perform the following operations after an effect from a voltage shift of the driving voltage terminal being coupled to the respective nodes of the driving circuit **300** is stabilized.

Meanwhile, the voltages of the nodes A and C are initialized as described above to maintain the first and second driving transistors 311 and 321 in a turn-on state when the threshold voltages of the first and second driving transistors 311 and 321 are compensated.

For example, for a threshold voltage compensation, it is necessary that the first and second driving transistors 311 and 321 are in a turn-on state. However, according to an example embodiment, the initial voltage is applied to the nodes A and C at the time of threshold voltage compensation, and thus, even if the driving voltage (VDD) is coupled and the voltages of the nodes A and C are raised to a certain extent as described above, the first and second driving transistors 311 and 321 may remain in the turn-on state. Accordingly, according to an example embodiment, the 45 initial voltage may be appropriately set in relation to the driving voltage (VDD).

The threshold voltage compensation duration is a duration for compensating the threshold voltages (Vth) of the first and second driving transistors 311 and 321. During the 50 threshold voltage compensation duration, both sixth and seventh threshold transistors 331 and 332 are turned off according to the control signal Emi, and thus the threshold voltage compensation may be carried out in the PAM driving circuit 310 and the PWM driving circuit 320 which are 55 independent of each other.

For example, during the threshold voltage compensation duration, the control signal RES remains in a low state, and thus the first and third transistors **312** and **322** may remain in a turn-on state. In addition, as described above with 60 reference to the initialization duration, the first and second driving transistors **311** and **312** may be in a turn-on state as well

Accordingly, when the voltage of the driving voltage terminal rises from the low voltage (-5V) to the driving voltage (VDD, +8V), the driving voltage (VDD) may be applied to the node A through the second driving transistor

20

321 and the third transistor 322 in a sequence and the threshold voltage compensation of the second driving transistor 321 may be initiated. Accordingly, when the voltage of the node A becomes the second voltage, the second driving transistor 321 may be turned off and the compensation of threshold voltage of the second driving transistor 321 may be ended.

When the voltage of the driving voltage terminal rises from the low voltage (-5V) to the driving voltage (VDD, +8V), the driving voltage (VDD) may be applied to the node C as well through the first driving transistor 311 and the first transistor 312 in a sequence. Accordingly, the threshold voltage compensation of the first driving transistor 311 may be initiated, and when the first voltage is applied to the voltage of the node C, the first driving transistor 311 may be turned off and the compensation of threshold voltage of the first driving transistor 311 may be ended.

When the compensation is ended, the nodes A and C may remain in a floating state.

The data voltage setup duration is a duration for respectively setting a data voltage to the PAM driving circuit **310** and the PWM driving circuit **320**.

According to an example embodiment, as illustrated in FIG. 10, the PWM data voltage setup may be performed first and then, the PAM data voltage setup may be performed. However, in an implementation, the order may be changed.

During the data voltage setup duration, both sixth and seventh transistors 331 and 332 are in a turn-off state according to the control signal Emi, and thus a data voltage may be set to the PAM driving circuit 310 and the PWM driving circuit 320 which are independent of each other.